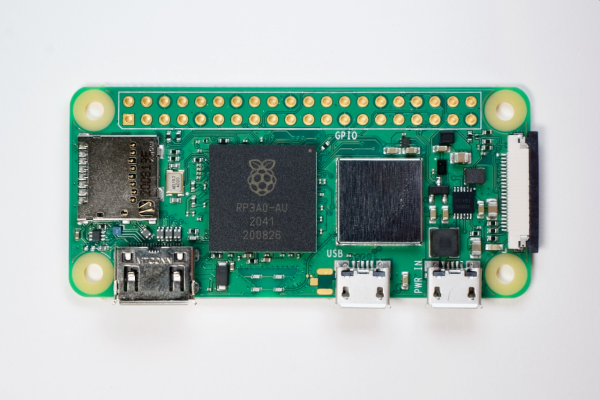

2021年10月に発表されてから8か月の月日が経ち、ようやく日本国内で発売開始されたRaspberry Pi Zero 2 W。

入荷連絡後に在庫が瞬溶けする中なんとか注文に成功したため、届くまでの間にいろいろと調べ物をしてみた。

CPUが強化されマルチスレッド性能は5倍以上に

Raspberry Pi 3と同じクアッドコアのCPUを搭載したことで、無印Zeroと比較してシングルスレッド性能は約1.4倍、マルチスレッド性能は5倍以上になったとのこと。

動作クロックは1.2→1GHzに下げられているが冷却すればオーバークロック可能。

SoCを除く各種スペック(寸法やポートなど)が旧機種のRaspberry Pi Zero Wと全く同じに揃えてあるため、ハードをそっくりそのままリプレースすることで性能強化できるのが心強い。

ラズパイのSoCは以前よりBroadcomのBCMxxxxシリーズが定番だが、今回のSoCの型番は「RP3A0」と見慣れない文字列。

何となくラズパイオリジナルっぽい型番だが、これは何だろうか。

ラズパイZero 2の新型SoC「RP3A0」とは

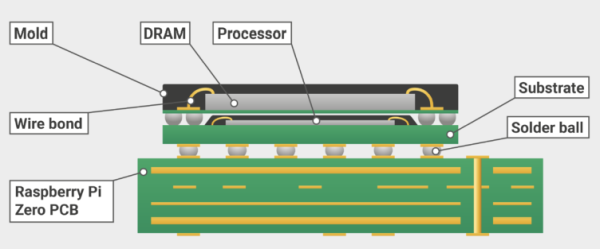

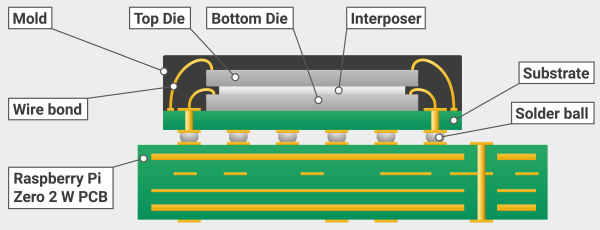

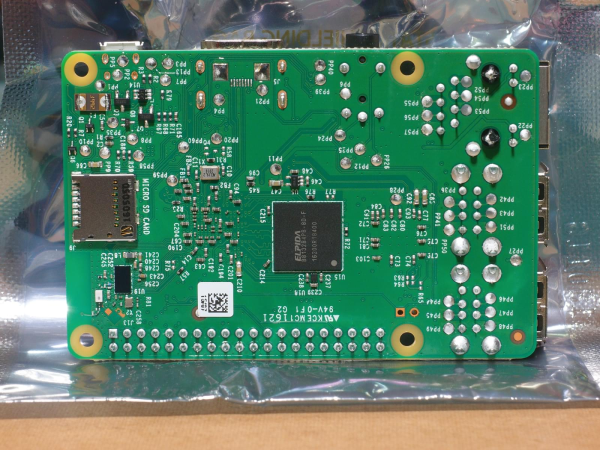

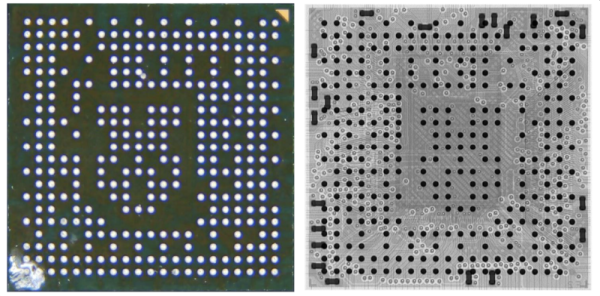

公式資料を見てみると、RP3A0は「BCM2837(ラズパイ3に搭載されているSoC)内部のシリコンダイ(半導体チップ)であるBCM2710A1と512MBのDRAMを1つのパッケージSystem-in-Package (SiP)にしたもの」と書かれている。

The Raspberry Pi RP3A0 is our first System-in-Package (SiP) consisting of a Broadcom BCM2710A1 - which is the silicon die packaged inside the Broadcom BCM2837 chip which is used on the Raspberry Pi 3 - along with 512MB of DRAM.

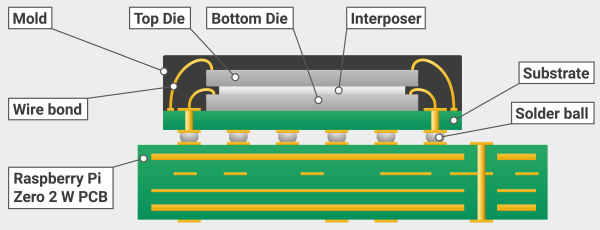

ご丁寧に図があるため確認すると、確かに黒いモールド(樹脂)の中にTop Die(=DRAM)とBottom Die(=BCM2710A1)の2枚のシリコンダイが描かれている。

このように、1つのパッケージ内に2つの半導体を共存させるのがSystem-in-Package (SiP)ということらしい。

ミソは「2枚重ね構造」

RP3A0の説明の下には「無印ラズパイZeroはPackage-on-Package (PoP)手法によってDRAMがBCM2835の真上に実装されている」と注釈がある。

NOTE

The original Raspberry Pi Zero uses Package-on-Package (PoP) DRAM, where the DRAM is soldered directly on top of the BCM2835 chip.

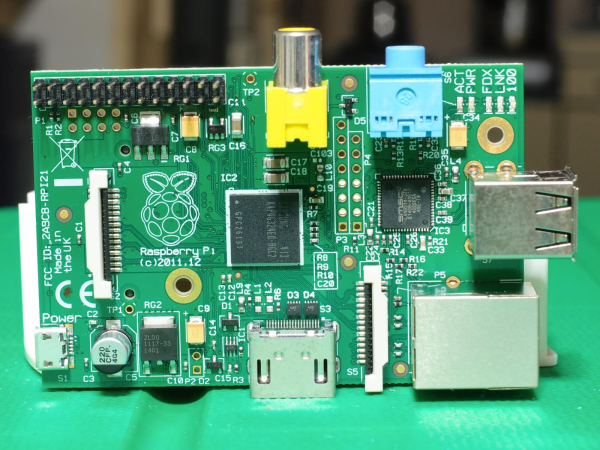

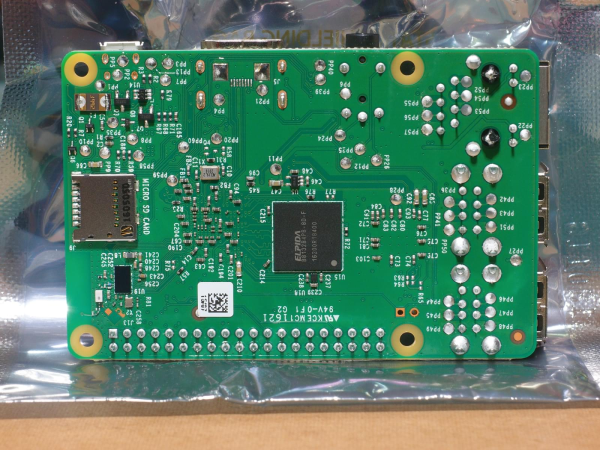

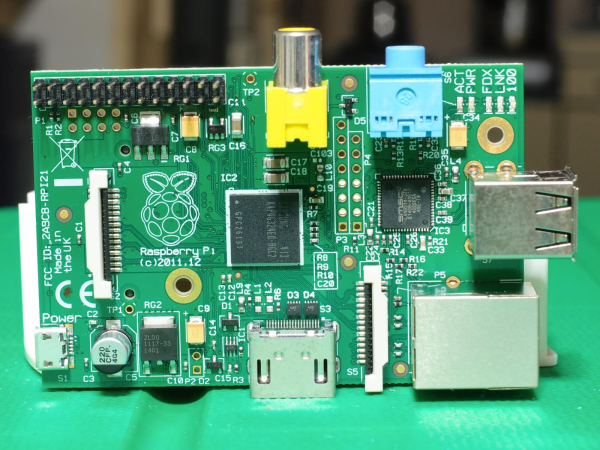

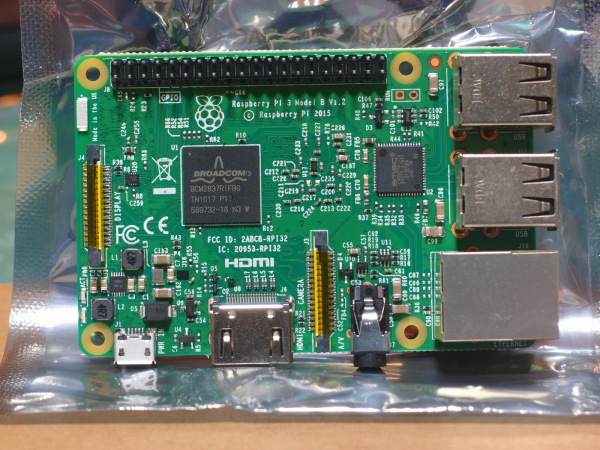

確かに旧ラズパイZeroやその親である初代ラズパイの基板を見ると、表面にはSAMSUNGやELPIDAと書かれたDRAMしか見えない。

(↑画像は古典コンピュータ愛好会より)

ではSoCはどこにあるのかというと、その真下に重ねられているのだ。笑点の座布団の如く。もしくはビックマックのパティの如く。

そのため表面に見える位置にSoCは出てこない。

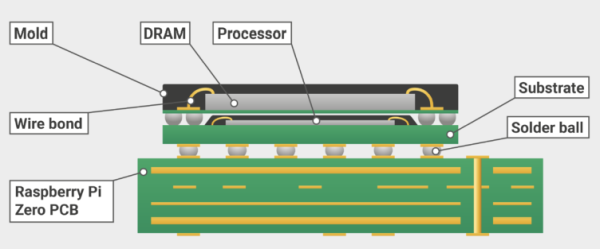

(↑セミコンポータルより)Package-on-Package (PoP)の例。

SoCのモールドが四角ではなく台形になっており、真上に他のICを実装できる。

ラズパイ2以降ではPoPは廃止されている

初代ラズパイはPoPによりSoCとDRAMを2枚重ねにしており、この効率のいい実装方法は無印ラズパイZeroにも引き継がれた。

(寧ろPoPが可能だったからこそコンパクトなラズパイZeroが生まれたともいえる)

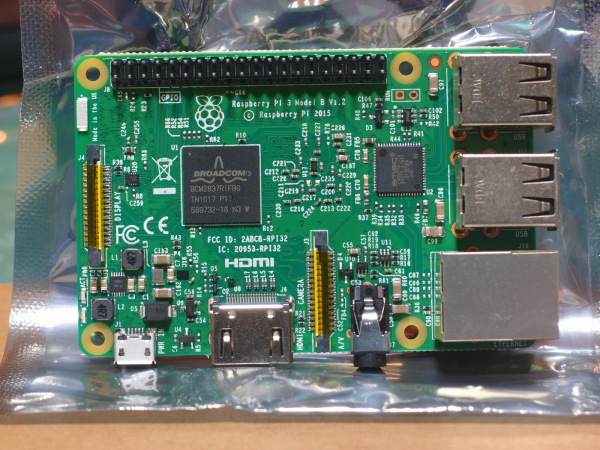

しかしラズパイ2,3,4を見ると、SoCとDRAMは別々に実装されるよう変わっていることが分かる。

(↑基板表面にはBroadcomのロゴが見える。これがSoC。古典コンピュータ愛好会より)

(↑基板裏面にはELPIDAのロゴが見える。これがDRAM。古典コンピュータ愛好会より)

では、どうしてラズパイ2以降ではPoPではなく別々に実装されるようになったのか。

PoPが採用されなくなった理由

初代ラズパイのBCM2835はシングルコアのプロセッサが搭載されているのに対し、ラズパイ2以降のSoCは4コアになったことでダイのサイズが大きくなってしまった。

これによりSoCの厚みがPoP実装可能サイズを超えてしまい、上にDRAMを載せることができなくなってしまったようだ。

Processor(SoC)とDRAMの間に許される隙間はBGAのはんだボール分しかない。

そのため、SoCの厚みがこれを超えてしまうと上にDRAMを実装することができなくなる。

このままでは実装スペースが足りない

つまりラズパイ2以降で採用された新しいSoCをラズパイZeroの基板上に持ってこようとしても、新しいSoCはこれまでのようにPoP実装できないため、SoCとDRAMを別々に実装する必要がある。

しかしラズパイの半分以下のフットプリントしかない上に片面実装のラズパイZeroにそんなスペースはない。どうすればいいか。

公式の供給がないなら、自分たちで重ねればいいじゃない

こうしてSiP技術のもと「RP3A0」は生まれた

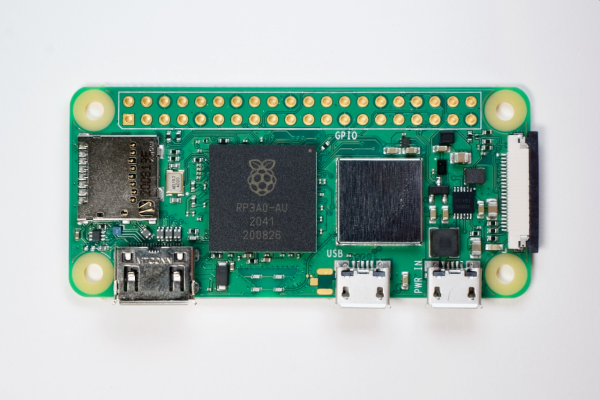

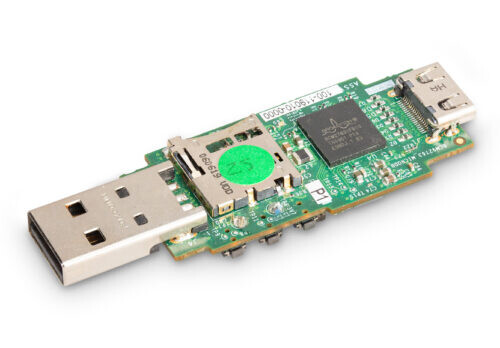

RP2040のような独自チップとは言えないものの、前述したSiP技術によりBroadcomのシリコンダイと既製品のDRAMを自分たちで独自にパッケージングすることで生まれた「RP3A0」。

Broadcomから買ったSoCをそのまま実装している他のラズパイと違い、独自パッケージングのため表面の刻印もラズパイのロゴになっている(RP2040に次ぎ2つ目)。

(↑Jeff Geerling氏の記事より)

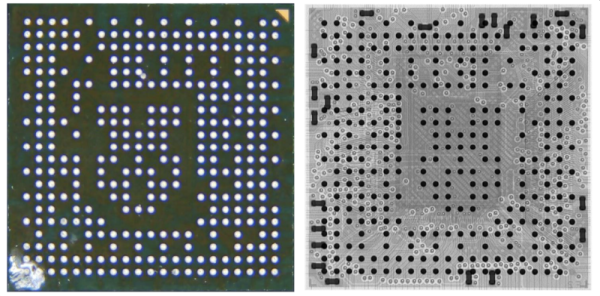

また実装面のBGAパターンにもラズパイのロゴが隠されている。

(Raspberry Pi公式サイトより)

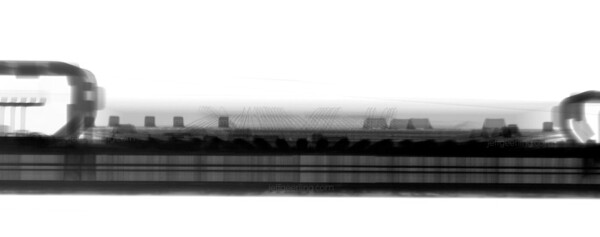

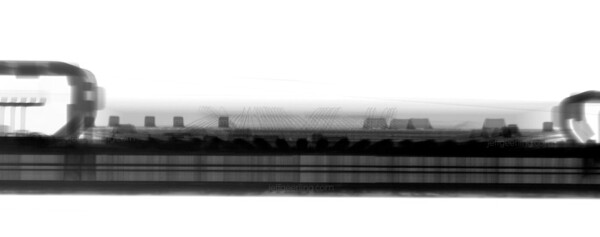

ちなみにJeff Geerling氏の記事ではRP3A0を横からX線撮影した写真を見ることができる。

とても細いボンディングワイヤが二種類あり、長い方が上のDRAMに、短い方が下のSoCに繋がっていることがなんとなく分かる。

(X線撮影環境を持っている氏は何者なんだろうか...)

メーカーでもないのにどうしてSiP技術を持っているのか

ここで一つ疑問が浮かび上がる。

半導体メーカーでもないラズパイチームはどうやってここまで手の込んだことを実現できたのか。

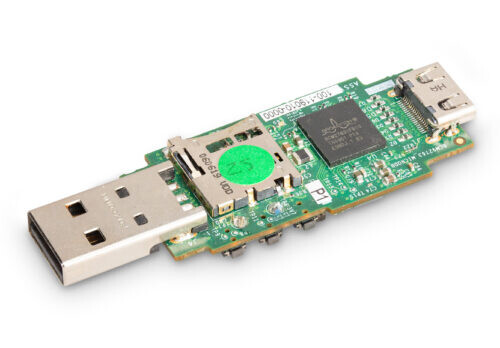

今回ラズパイZero2とRP3A0を設計したのはSimon Martin氏。

実はこの人、10年ほど前はBroadcomで働いており、BCM2835(初代ラズパイに搭載されているSoC)と128MB SDRAMを1つのパッケージに集約(SiP)したBCM2763を作っていたのだ。

(↑BCM2763を搭載したRaspberry Piのプロトタイプ。公式サイトより)

つまりSimon Martin氏は10年前に同じことをやり遂げた実績があり、その張本人によってRP3A0は生み出されたわけだ。

ここで驚くべきは「メーカーの中の人」をしっかり抱え込んでいるラズパイチーム。

最終製品を作るだけでなく、そこで使う部品まで自前で設計できるリソースを持っていることは「RP2040」の誕生によって世に知らしめられたことではあるが、改めてその凄さを目の当たりにすることになった。

メモリが512MBなのは残念だけど事情はよく分かった

ちなみに、CPU性能は大幅に上がったのにメモリが512MBから増えなかった理由もSiP実装によるものだそうで。

公式のFAQによるとLPDDR2のダイは1つ512MBのものしかないため、もし1GBを搭載しようとするとSoC+512MB+512MBの3階建てになってしまう。

これは非常に困難("very challenging")とのことで、やむを得ないだろう。むしろこれだけ実装が困難な中でCPUが強化されただけでも喜ばしいことである。

ちなみにWikipediaの定義では

- SoCは「集積回路の1個のチップ上に複数機能を集積したもの」

- SiPは「複数のLSIチップを1つのパッケージ内に封止したもの」

とあり、今回の「RP3A0」は「SoCであるBCM2710A1とDRAMをSiP化した製品」だといえる。

と思うのだが、SiPのページに「SiPの対語はSOC」と書かれている。SiPとSoCは相反するものなんだろうか。

しかしSoCのページには「状況によって使い分けたり、SoCとSiPを組み合わせて用いたりする」と書かれているので「SiPの対語はSOC」は誤りのような気がするが、専門外なのでよく分からない。

その他の参考リンク:

コメントする